Verilog Mux Modeling: Ternary operator or “if” statement?

Posted by enfilade3 in Uncategorized on October 10, 2013

While you can model a mux in verilog using both ternary operator or “if” statement

always_comb out_sel = sel ? in_1 : in_0; //Ternary Operator

always_comb //If Statement

begin

if (sel)

out_sel = in_1;

else

out_sel = in_0;

end

and though both are functionally equivalent, there is an advantage in using ternary operator as far as ‘X’ propagation is concerned.

Consider sel == X and in_0 == 0 & in_1 == 1; in this case out_sel == X when ternary operator is used, whereas out_sel == 0 for ‘if’ statement.

Thus the ternary operator will propagate the X’s in a sensible way (enabling easy debug) whereas ‘if’ statement considers X as if it were ‘0’ thereby masking potential RTL problems. The choice is yours…

False Path – Design Example

Posted by enfilade3 in Uncategorized on March 20, 2013

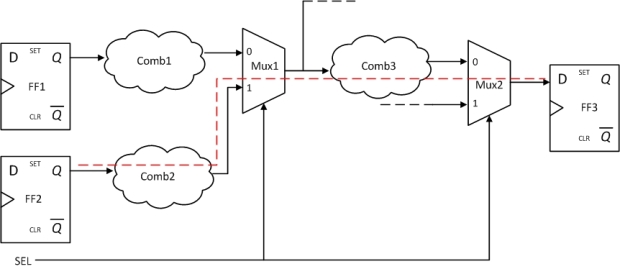

A false path is a physical path that is never functionally accessed by the design. An example for the same is shown below:

The highlighted path (FF2 -> Comb2 -> Mux1 -> Comb3 -> Mux2 -> FF3) can never be accessed by the design since SEL is shared by Mux1 & Mux2, and when SEL = 1, Mux2 chooses a different path. But the same path can be reported for timing violations by the synthesis/timing tools. So we have to enlighten these tools about the path by using ‘set_false_path’ command.

Multicycle Path – Design Example

Posted by enfilade3 in Uncategorized on March 17, 2013

A multicycle path is a flop-to-flop path where the logic delay in between the flops is permissible to take more than one clock cycle as per the design. An example for this is shown below:

As can be seen from figure, the multiplier (Path1 & Path2) can take two clock cycles to compute the output (ensured by the flopped enable signal) unlike the other logic paths – Q11->Combo1->D21, Q21->Combo1->D21, Q12->Combo3->D31 etc. The timing diagram for the same is also shown below for more clarity

The output Q32 changes in every two cycles. The synthesis/Timing tools have to be informed about this constraint using set_multicycle_path command. Else these tools will try to meet the timing through multiplier in one clock cycle, resulting in false timing violations, area increase etc